## Parallel Cryptanalysis

Ruben Niederhagen

#### Parallel Cryptanalysis

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op maandag 23 april 2012 om 16.00 uur

door

Ruben Falko Niederhagen

geboren te Aken, Duitsland

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. T. Lange en prof.dr. D.J. Bernstein

Copromotor: dr. C.-M. Cheng

A catalogue record is available from the Eindhoven University of Technology Library. ISBN: 978-90-386-3128-8

Printed by Printservice Technische Universiteit Eindhoven Cover design by Verspaget & Bruinink, Nuenen

Public domain

#### Commissie:

prof.dr. D.J. Bernstein, promotor (University of Illinois at Chicago)

dr. C.-M. Cheng, copromotor (National Taiwan University)

prof.dr. A.M. Cohen, chairman

prof.dr. R. Bisseling (Utrecht University)

prof.dr. T. Lange, promotor

prof.dr. W.H.A. Schilders

prof.dr. G. Woeginger

prof.dr. B.-Y. Yang (Academia Sinica)

#### Acknowledgements

I would like to thank my supervisors Daniel J. Bernstein and Tanja Lange as well as my supervisors in Taiwan, Chen-Mou Cheng and Bo-Yin Yang, for the opportunity to enjoy my PhD studies commuting between the Netherlands and Taiwan. Furthermore, I would like to thank them for their support throughout my studies and the writing of my thesis.

I also would like to thank Rob Bisseling, Arjeh Cohen, Wil Schilders, and Gerhard Woeginger for joining my doctorate committee and for their valuable feedback on the draft of my dissertation.

Special thanks go to Tung Chou, Andreas Gierlich, and Peter Schwabe for proofreading of the first versions of my thesis and for suggesting corrections and improvements.

Finally, I want to thank Stefan Lankes from the Lehrstuhl für Betriebssysteme (research group for operating systems) at RWTH Aachen University for his support in the first years of my PhD studies.

## Contents

| 1 | Intr                     | oduct                          | ion                                                    | 1  |  |  |

|---|--------------------------|--------------------------------|--------------------------------------------------------|----|--|--|

| 2 | Ove                      | Overview of parallel computing |                                                        |    |  |  |

|   | 2.1                      | Parall                         | el architectures                                       | Ę  |  |  |

|   |                          | 2.1.1                          | Microarchitecture                                      | Ę  |  |  |

|   |                          | 2.1.2                          | Instruction set                                        | 7  |  |  |

|   |                          | 2.1.3                          | System architecture                                    | 8  |  |  |

|   | 2.2 Parallel programming |                                |                                                        |    |  |  |

|   |                          | 2.2.1                          | Shared memory                                          | 12 |  |  |

|   |                          | 2.2.2                          | Message passing                                        | 14 |  |  |

|   |                          | 2.2.3                          | Summary                                                | 14 |  |  |

|   | 2.3                      | Gener                          | al-purpose GPU programming                             | 15 |  |  |

|   |                          | 2.3.1                          | Programming NVIDIA GPUs                                | 17 |  |  |

|   |                          | 2.3.2                          | Assembly for NVIDIA GPUs                               | 18 |  |  |

| 3 | Par                      | allel ir                       | nplementation of Pollard's rho method                  | 23 |  |  |

| • | 3.1                      |                                | CCDLP and the parallel version of Pollard's rho method | 24 |  |  |

|   | 3.2                      |                                | K-130 and the iteration function                       | 25 |  |  |

|   | 3.3                      |                                | menting ECC2K-130 on the Cell processor                | 26 |  |  |

|   | 0.0                      | 3.3.1                          | A Brief Description of the Cell processor              | 27 |  |  |

|   |                          | 3.3.2                          | Approaches for implementing the iteration function     | 29 |  |  |

|   |                          | 3.3.3                          | ECC2K-130 iterations on the Cell processor             | 31 |  |  |

|   |                          | 3.3.4                          | Using DMA transfers to increase the batch size         | 33 |  |  |

|   |                          | 3.3.5                          | Overall results on the Cell processor                  | 34 |  |  |

|   | 3.4                      | Imple                          | menting ECC2K-130 on a GPU                             | 35 |  |  |

|   |                          | 3.4.1                          | The GTX 295 graphics card                              | 36 |  |  |

|   |                          | 3.4.2                          | Approaches for implementing the iteration function     | 38 |  |  |

|   |                          | 3.4.3                          | Polynomial multiplication on the GPU                   |    |  |  |

|   |                          | 3.4.4                          | ECC2K-130 iterations on the GPU                        |    |  |  |

|   |                          | 3.4.5                          | Overall results on the GPU                             | 44 |  |  |

|   | 3.5                      | Porfor                         | rmanco comparison                                      | 45 |  |  |

| 4  | Par   | llel implementation of the XL algorithm                       |  | 47           |

|----|-------|---------------------------------------------------------------|--|--------------|

|    | 4.1   | The XL algorithm                                              |  |              |

|    | 4.2   | The block Wiedemann algorithm                                 |  | 49           |

|    | 4.3   | The block Berlekamp–Massey algorithm                          |  | 53           |

|    |       | 4.3.1 Reducing the cost of the Berlekamp–Massey algorithm .   |  | 54           |

|    |       | 4.3.2 Parallelization of the Berlekamp–Massey algorithm       |  | 55           |

|    | 4.4   | Thomé's version of the block Berlekamp–Massey algorithm       |  | 58           |

|    |       | 4.4.1 Matrix polynomial multiplications                       |  | 58           |

|    |       | 4.4.2 Parallelization of Thomé's Berlekamp–Massey algorithm   |  | 58           |

|    | 4.5   | Implementation of XL                                          |  | 59           |

|    |       | 4.5.1 Reducing the computational cost of BW1 and BW3          |  | 60           |

|    |       | 4.5.2 SIMD vector operations in $\mathbb{F}_{16}$             |  | 60           |

|    |       | 4.5.3 Exploiting the structure of the Macaulay matrix         |  | 62           |

|    |       | 4.5.4 Macaulay matrix multiplication in XL                    |  | 64           |

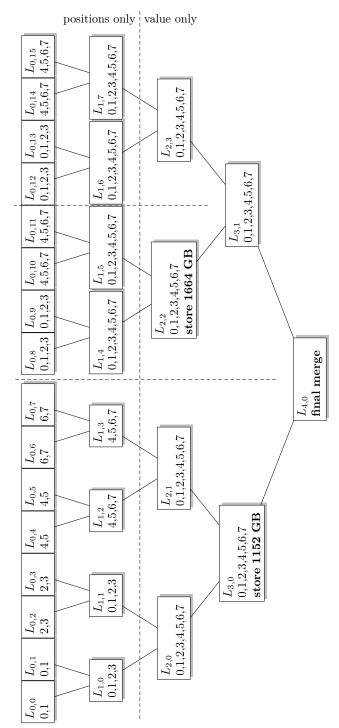

|    |       | 4.5.5 Parallel Macaulay matrix multiplication in XL           |  | 66           |

|    | 4.6   | Experimental results                                          |  | 73           |

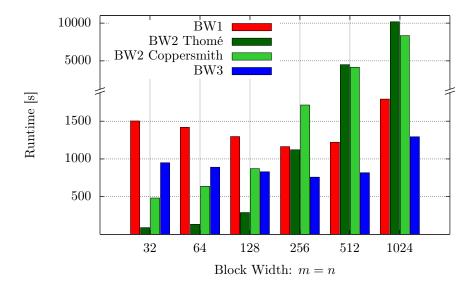

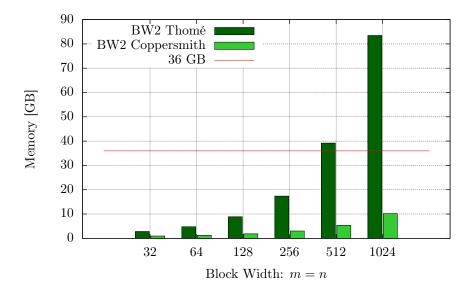

|    |       | 4.6.1 Impact of the block size                                |  | 74           |

|    |       | 4.6.2 Performance of the Macaulay matrix multiplication       |  | 76           |

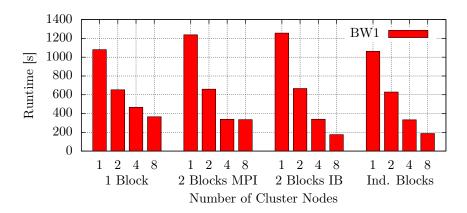

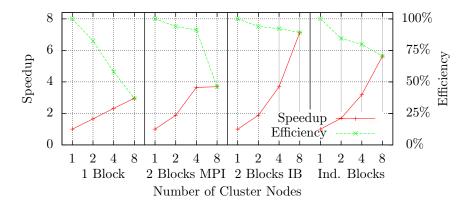

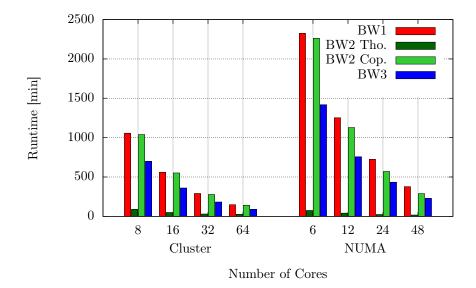

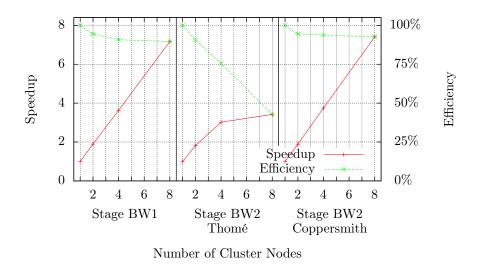

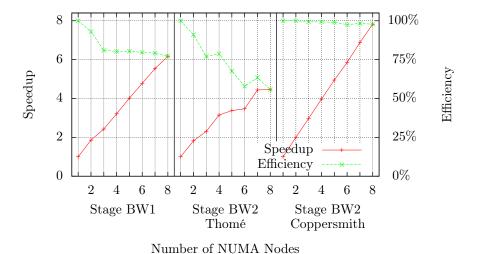

|    |       | 4.6.3 Scalability experiments                                 |  | 78           |

| _  | ъ.    | 11 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                      |  | 01           |

| 5  |       | llel implementation of Wagner's birthday attack               |  | <b>81</b> 82 |

|    | 5.1   | Wagner's generalized birthday attack                          |  |              |

|    |       | 5.1.1 Wagner's tree algorithm                                 |  |              |

|    | 5.2   | The FSB hash function                                         |  |              |

|    | 3.2   | 5.2.1 Details of the FSB hash function                        |  |              |

|    |       | 5.2.2 Attacking the compression function of FSB <sub>48</sub> |  |              |

|    | 5.3   | ·                                                             |  |              |

|    | 5.5   | Attack strategy                                               |  |              |

|    |       | 5.3.1 How large is a list entry?                              |  |              |

|    |       |                                                               |  |              |

|    | 5.4   | 92                                                            |  |              |

|    | 5.4   | Implementing the attack                                       |  |              |

|    |       |                                                               |  |              |

|    | ==    | 1                                                             |  |              |

|    | 5.5   | Results                                                       |  |              |

|    |       |                                                               |  |              |

|    |       |                                                               |  |              |

|    | 5.6   | O .                                                           |  |              |

|    | 5.6   | Scalability analysis                                          |  | 98           |

| Bi | bliog | raphy                                                         |  | 101          |

# Introduction

Most of today's cryptographic primitives are based on computations that are hard to perform for a potential attacker but easy to perform for somebody who is in possession of some secret information, the key, that opens a back door in these hard computations and allows them to be solved in a small amount of time. Each cryptographic primitive should be designed such that the cost of an attack grows exponentially with the problem size, while the computations using the secret key only grow polynomially. To estimate the strength of a cryptographic primitive it is important to know how hard it is to perform the computation without knowledge of the secret back door and to get an understanding of how much money or time the attacker has to spend. Usually a cryptographic primitive allows the cryptographer to choose parameters that make an attack harder at the cost of making the computations using the secret key harder as well. Therefore designing a cryptographic primitive imposes the dilemma of choosing the parameters strong enough to resist an attack up to a certain cost while choosing them small enough to allow usage of the primitive in the real world, e.g. on small computing devices like smart phones.

Typically a cryptographic attack requires a tremendous amount of computation—otherwise the cryptographic primitive under attack can be considered broken. Given this tremendous amount of computation, it is likely that there are computations that can be performed in parallel. Therefore, parallel computing systems are a powerful tool for the attacker of a cryptographic system. In contrast to a legitimate user who typically exploits only a small or moderate amount of parallelism, an attacker is often able to launch an attack on a massively parallel system. In practice the amount of parallel computation power available to an attacker is limited only by the amount of money he is able to spend; however the

amount of parallelism he can exploit depends on the particular attack which he is going to mount against a particular cryptographic primitive. The main challenge of implementing a cryptographic attack for a parallel computing system is to explore which parts of the computation can be computed in parallel and how this parallelism can be exploited most efficiently.

This thesis investigates three different attacks on particular cryptographic systems: Wagner's generalized birthday attack is applied to the compression function of the hash function FSB. Pollard's rho algorithm is used for attacking Certicom's ECC Challenge ECC2K-130. The implementation of the XL algorithm has not been specialized for an attack on a specific cryptographic primitive but can be used for attacking certain cryptographic primitives by solving multivariate quadratic systems. All three attacks are general attacks, i.e. they apply to various cryptographic systems; therefore the implementations of Wagner's generalized birthday attack and Pollard's rho algorithm can be adapted for attacking other primitives than those given in this thesis. The three attacks have been implemented on parallel architectures, each attack on a different architecture. The results give an estimate of the scalability and cost of these attacks on parallel systems.

#### Overview

Chapter 2 gives an introduction to parallel computing. The work on Pollard's rho algorithm described in Chapter 3 is part of a large research collaboration with several research groups; the computations are embarrassingly parallel and are executed in a distributed fashion in several facilities on a variety of parallel system architectures with almost negligible communication cost. This dissertation presents implementations of the iteration function of Pollard's rho algorithm on Graphics Processing Units and on the Cell Broadband Engine. Chapter 4 describes how XL has been parallelized using the block Wiedemann algorithm on a NUMA system using OpenMP and on an InfiniBand cluster using MPI. Wagner's generalized birthday attack is described in Chapter 5; the attack has been performed on a distributed system of 8 multi-core nodes connected by an Ethernet network.

## 2

### Overview of parallel computing

Parallelism is an essential feature of the universe itself; as soon as there exists more than one entity and there is interaction between these entities, some kind of parallel process is taking place. This is the case for quantum mechanics as well as astrophysics, in chemistry and biology, in botanics and zoology, and human interaction and society. Therefore, exploiting parallelism also in information technology is natural and has started already at the beginning of modern computing.

The main condition for parallel computing is that there are parts of the computation which can be executed in parallel. This is the case if there are at least two parts of the computation which have no data dependencies, i.e., the input data of each part is not depending on the result of the computation of the other part. In [LS08], Lin and Snyder classify parallelism into two types as follows:

- In case the same sequence of instructions (e.g., the same mathematical function) is applied to a set of independent data items, the computation on these data items can be performed in any order and therefore, in particular, in parallel. This kind of parallelism is called *data parallelism*. The amount of parallelism scales with the number of independent data items.

- Some computations can be split in several tasks, i.e., independent instruction sequences which compute on independent data items. Since the tasks are independent from each other, they can be computed in parallel. This is called *task parallelism*. The number of independent tasks for a given computation is fixed and does not scale for a larger input.

Given that a program exhibits some parallelism, this parallelism can be exploited on a parallel computer architecture. In [Fly66] Flynn classifies computer

architectures with respect to their ability to exploit parallelism by looking at the *instruction stream*, the sequence of instructions that are executed by a computer, and the *data stream*, the sequence of data that is processed by the instruction stream. Using these two terms, Flynn defines the following categories of parallel computer architectures:

- Single Instruction Stream Single Data Stream (SISD): The computer follows only one instruction stream that operates on data from one single data stream.

- Single Instruction Stream Multiple Data Streams (SIMD): Each instruction of the instruction stream is executed on several data streams.

- Multiple Instruction Streams Single Data Stream (MISD): Several instructions from different instruction streams are executed on the same single data stream.

- Multiple Instruction Streams Multiple Data Streams (MIMD): Instructions from different instruction streams are applied to independent data streams.

Data parallelism can naturally be exploited on SIMD architectures. By duplicating the instruction stream it also fits to MIMD architectures. Task parallel applications are usually suitable for MIMD architectures.

MISD architectures are merely stated for theoretical completeness. Nevertheless, one may argue that MISD architectures are used, e.g., for fault detection (although in this case the same instruction stream would be executed multiple times on the same data stream) or in pipelining systems (although one may argue that the data changes after each instruction).

Many applications exhibit data parallelism as well as task parallelism. Therefore, many computer systems incorporate SIMD and MIMD techniques and are able to perform mixed data and task parallel workloads efficiently.

The reason for spending effort in exploiting parallelism is to gain some speedup in the execution. For a given task, the speedup S is defined as the ratio between the time  $t_s$  of execution for the sequential, non-parallelized implementation and the time  $t_p$  of execution in parallel:

$$S = \frac{t_s}{t_p}.$$

The optimal speedup on n execution units therefore is

$$S_{\text{optimal}} = \frac{t_s}{\frac{t_s}{n}} = n.$$

However, when running a program on a computer, not all instructions may be able to be executed in parallel due to dependencies. The improvement one can gain from parallelism in terms of speedup is restricted according to Amdahl's law (as proposed by Amdahl in [Amd67]): let p be the part of the program that can

be executed in parallel and s the part that must be executed sequentially, i.e., p + s = 1; the best speedup possible when using n execution units is

$$S = \frac{1}{s + \frac{p}{s}}.$$

Consequently, a high gain in speedup can only be reached if the sequential part of a program is sufficiently small. In case s is equal or extremely close to zero the program is called *embarrassingly parallel*. If s is too large, adding more and more execution units does not give noticeable benefit.

Amdahl's law seems to suggest that it is not worth to split workload over hundreds or even thousands of execution units if the sequential part is not negligible. However, that is not necessarily the case. Amdahl assumes the problem size to be fixed. In [Gus88] Gustafson points out that for many scientific applications a higher number of execution units gives the opportunity to increase the problem size and thus to get more accurate results. When scaling the problem size, for many applications the sequential part remains almost the same while the parallel part increases. In case the workload scales linearly with the number of execution units, an estimate of the speedup can be obtained from Gustafson's law [Gus88] as

$$S = \frac{s + np}{s + p} = s + np = n + s(1 - n).$$

In cryptanalytic applications the problem size is usually fixed, for example an attack on an encryption using a certain encryption standard with a certain parameter set. Nevertheless, the problem size and therefore the workload naturally is very large. Thus, cryptanalytic applications are good candidates for parallelization—given that they exhibit a sufficient amount of parallelism.

#### 2.1 Parallel architectures

There are many types of parallel architectures, which mainly differ in the physical distance between the execution units. The distance gives a lower bound on the time that is required to deliver information from one unit to another. Therefore it has a big impact on how data is exchanged between the execution units and how communication is accomplished. This section introduces parallel architectures on the level of the microarchitecture, the instruction set, and the system architecture.

#### 2.1.1 Microarchitecture

The microarchitecture of a processor is the lowest level on which computations can be executed in parallel. The microarchitecture focuses on the computation of a single instruction stream. If a sequential instruction stream contains one or more instructions that operate on different data items, i.e., if each input does not depend on the output of another one, these instructions can be executed in any order and therefore in parallel. This kind of parallelism is called *instruction level parallelism*.

#### Instruction pipelining

The execution of any instruction can be split into several stages [HP07, Appendix A]: for example it is split into instruction fetch, instruction decode, execution, memory access, and write back of results to the output register. For different instructions the execution stage might take a different amount of time depending on the complexity of the instruction: for example an XOR-instruction typically takes less time than a double-precision floating-point multiplication.

If all these stages were executed in one single clock cycle of a fixed length, much time would be wasted on the faster instructions since the processor would need to wait as long as the slowest instruction needs to finish. Furthermore, while an instruction is processed, e.g., by the execution unit all other stages would be idle.

Instead, the processor frequency and instruction throughput can be increased by pipelining the different stages of the instruction execution and by splitting the execution stage in several clock cycles depending on instruction complexity. After the first instruction has been loaded, it is forwarded to the decoder which can decode the instruction in the next cycle. At the same time, the second instruction is loaded. In the third cycle the first instruction starts to be executed while the second one is decoded and a third one is loaded in parallel.

This requires all instructions which are in the pipeline at the same time to be independent from each other; in case the instructions lack instruction level parallelism, parts of the pipeline have to stall until all dependencies have been resolved.

There are two ways to achieve a high throughput of instructions: Either the instructions are scheduled by a compiler or by the programmer in a way that minimizes instruction dependencies on consecutive instructions in a radius depending on the pipeline length. Or the fetch unit looks ahead in the instruction stream and chooses an instruction for execution which is independent from the instructions that are currently in the pipeline; this is called *out-of-order execution*. Details on out-of-order execution can be found in [HP07, Section 2.4].

The physical distance between the pipeline stages is very small and the communication time between the stages can almost be neglected. From the outside a pipelined processor appears to be a SISD architecture; internally the pipeline stages actually resemble a MIMD architecture.

#### Superscalar processors

Another way to exploit instruction level parallelism is to use several arithmetic logic units (ALUs) to compute an instruction stream. An instruction scheduler forwards several independent instructions to several ALUs in the same clock cycle. The ALUs may share one common instruction set or they may have different instruction sets, e.g., a processor may have two integer units and one floating point unit. As in the case of pipelining, the instruction scheduler of a superscalar processor may examine several upcoming instructions out of order to find independent instructions.

The ALUs communicate directly through registers without communication costs; after the output of one instruction has been computed it is usually available for all ALUs in the following cycle. Similar to pipelining architectures, superscalar processors appear to be SISD architectures but internally they operate in an MIMD fashion.

Instruction pipelining as well as superscalar execution is very common and used in most of today's microarchitectures like the x86 and AMD64 processors from Intel and AMD, IBM's PowerPC processors and so on. Both approaches are often combined: several stages of the instruction pipeline can be duplicated to allow parallel execution of independent instructions.

The drawback of these architectures is that they lose performance if there is not enough instruction level parallelism available or found during compilation or execution. In particular programs that have many conditions or branches suffer from these techniques. Furthermore, the logic for instruction scheduling and dependency detection consumes resources which are not available for execution units any more.

Another type of parallelism that can be exploited by a microarchitecture is bit level parallelism: Processors handle data in units of a certain number of bits, the word size. By increasing the word size a processor is able to compute on more data in parallel: a processor of a word size of 64 bits can compute an addition of two 64-bit numbers using one instruction, a 32-bit processor would need at least two instructions plus possibly more instructions to handle overflows. For example the x86 processor architecture started with a word size of 16 bits in 1978, was extended to 32 bits in the mid eighties, and eventually supported a word size of 64 bits with the introduction of the Pentium 4F processor in 2004.

#### 2.1.2 Instruction set

Microarchitectures mainly aim at the exploitation of instruction level parallelism. However, the instruction set of a single processor may also offer parallelism which can be exploited either by the programmer or by a compiler.

#### Vector processors

Vector processors implement the SIMD architecture: the same instruction is executed on independent data elements (vector elements) from several data streams in parallel. The elements are loaded into vector registers which consist of several slots, one for each data element. Vector instructions, often called SIMD instructions, operate on the vector registers.

The number of execution units does not necessarily need to be equal to the number of vector elements. The processor may operate only on parts of the vector registers in each clock cycle. Usually vector processors only have 4 (e.g., NEC SX/8) to 8 (e.g., Cray SV1) ALUs (see [HP07, Appendix F]). Nevertheless, operating on a large vector in several steps on groups of the vector register slots

allows the processor to hide instruction and memory latencies: since it takes several cycles before the execution on the last group of register slots has started, the operation on the first group is likely to be finished so that all dependencies that might exist for the next instruction are resolved.

Initially, a very high number of vector elements was envisioned, for example as much as 256 elements for the early prototype architecture Illiac IV (which eventually was built with only 64 vector elements) [BDM<sup>+</sup>72]. The Cray-1 had 8 vector registers of 64 vector elements each as well. Today, many specialized scientific computers also offer wide vector registers of 64 to 256 vector elements [HP07, Figure F.2].

Apart from these cases also short-vector architectures are very common. Most of today's x86-processors have 128-bit vector registers, which can be used for 8-, 16-, 32-, or 64-bit vector operations on sixteen, eight, four, or two vector elements. The Synergistic Processing Units of the Cell processor have a similar design and the PowerPC processors also provide 128-bit vector registers. Note that 128-bit vector registers can also be used for 1-bit operations, i.e. logical operations, on 128 vector elements. This is exploited by a technique called bitslicing; see Chapter 3 for an application of this technique.

#### Very Long Instruction Word processors

Superscalar processors exploit instruction level parallelism by choosing several data-independent instructions from the instruction stream for execution. The logic for this run-time instruction scheduling is relatively complex and consumes extra resources. But the scheduling of instructions can also be done off-line: the compiler or the programmer schedules independent instructions into instruction groups that can be forwarded by the fetch unit at once to several ALUs. Therefore, the ALUs can be kept busy without the need for dedicated scheduling hardware. This architecture is called *Very Long Instruction Word (VLIW)*.

VLIW processors are not easily classified by Flynn's taxonomy. On a large scale, a single instruction stream operates on a single data stream. However, due to the fact that VLIW processors contain several ALUs they may also be categorized as MIMD or even MISD architectures. VLIW processors were first mentioned by Fisher in 1983 [Fis83] but have not been widely deployed before the IA-64 architecture by HP and Intel and its implementation as Intel Itanium processor starting in 2001 (see [HP07, Appendix G]). The most recent, widespread VLIW processors are the graphics processing units of AMD.

#### 2.1.3 System architecture

On a large scale, a parallel architecture can be designed by connecting several execution units by a variety of network interconnects and/or system buses. The following paragraphs give a short introduction to several parallel system architectures.

#### Symmetric Multiprocessing

Several execution units can be connected by a system bus. If all execution units have the same architecture, this system architecture is called *Symmetric Multiprocessing* (SMP). All execution units of an SMP architecture share a joint memory space.

Multi-core processors: A multi-core processor consists of several execution units called *cores* which compute in an MIMD fashion. Several resources might be shared, such as (parts of) the cache hierarchy as well as IO and memory ports. The operating system has access to all cores and schedules processes and threads onto the cores. Communication between the cores can be accomplished via shared cache or via main memory.

Almost all of today's high-end CPUs are multi-core CPUs. Multi-core processors are used in a large range of devices: servers, desktop PCs, even embedded systems and mobile phones are powered by multi-core processors. Common configurations range from dual-core CPUs to ten- and even twelve-core CPUs (in May 2011). Core count of mainstream processors is envisioned to raise even higher, even though up to now only a small fraction of desktop applications benefit from multi-core architectures.

Non-Uniform Memory Access: If several conventional processors are placed on one mainboard and are connected by a system bus, each processor has a memory controller of its own even though all processors have full access to all memory. Since latency as well as throughput may vary depending on which physical memory is accessed, this architecture is called *Non-Uniform Memory Access* (NUMA) architecture as opposed to *Uniform Memory Access* (UMA) architectures (for example multi-core processors) where accessing any physical memory address has the same performance. Several multi-core processors may be used to set up a NUMA system.

Since the mainboards for NUMA systems are more expensive than off-the-shelf boards, NUMA systems are usually used for commercial or scientific workloads. The communication distance between the execution units is higher than in the case of multi-core processors since caches are not shared and all communication must be accomplished via main memory.

Simultaneous multithreading: In general a lack of instruction level parallelism on pipelined or superscalar processors as well as high-latency instructions (like memory access or IO) may lead to stalls of one or several ALUs. This can be compensated for by a technique called *simultaneous multithreading* (SMT): A processor with an SMT architecture concurrently computes two or more instruction streams, in this case called processes or threads. Therefore the instruction scheduler has more options to choose an instruction from one of the independent instruction streams. For concurrent execution, each instruction stream requires his own instance of resources like the register file. In contrast to multi-core processors, simultaneous multithreading is not really a parallel architecture even though it appears to be a MIMD architecture from the outside. Actually, it just allows a higher exploitation of the computation resources of a single processor.

Since each thread has its own register file, communication between the instruction streams is accomplished via memory access. In the best case, shared data can be found in on-chip caches but communication might need to be channeled via main memory.

SMT is state of the art in many of today's processors. Usually, two concurrent threads are offered. Intel calls its SMT implementation *Hyper-Threading Technology* (HTT) and uses it in most of its products. AMD, IBM and others use SMT as well.

#### Accelerators

Using accelerators in contrast to SMP architectures leads to a heterogeneous system design. Accelerators can be any kind of computing device in addition to a classical processor. Either the accelerators are connected to the processor via the system bus as for example in the case of Field-Programmable Gate Array (FPGA) cards and graphics cards or they can be integrated onto the die of the processor like the Synergistic Processing Elements of the Cell processor, Intel's E600C Atom chips with integrated FPGAs, or the Fusion processors of AMD, which include Graphics Processing Units (GPUs); there is a strong trend for moving accelerators from the system bus into the processor chip.

Parallel computing on FPGAs is not part of this thesis and therefore will not be further examined; GPUs will be described in more detail in Sections 2.3 and 3.4.1, the Cell processor in Section 3.3.1.

#### Supercomputers

The term *supercomputer* traditionally describes a parallel architecture of tightly coupled processors where the term *tight* depends on the current state of the art. Many features of past supercomputers appear in present desktop computers, for example multi-core and vector processors. Today's state of the art supercomputers contain a large number of proprietary technologies that have been developed exclusively for this application. Even though supercomputers are seen as a single system, they fill several cabinets or even floors due to their tremendous number of execution units.

Since supercomputers are highly specialized and optimized, they have a higher performance compared to mainstream systems. On the TOP500 list of the most powerful computer systems from November 2011 only 17.8% of the machines are supercomputers but they contribute 32.16% of the computing power. The machines of rank one and two are supercomputers. Even though the number of supercomputers in the TOP500 list has been declining of the past decade, they still are the most powerful architectures for suitable applications. The TOP500 list is published at [MDS+11].

Supercomputers are MIMD architectures even though they commonly are treated as *Single Program Multiple Data (SPMD)* machines (imitating Flynn's taxonomy): the same program is executed on all processors, each processor handles

a different fraction of the data, and communication is accomplished via a high-speed interconnect. In general, supercomputers provide a large number of execution units and fast communication networks, which make them suitable for big problem instances of scientific computations.

#### Cluster computing

Off-the-shelf desktop computers or high-end workstations can be connected by a high-speed interconnect to form a *computer cluster*. Classical high-speed interconnects are InfiniBand and Myrinet; Gigabit-Ethernet is becoming more and more widespread as well. Several clusters can be coupled by a wide area network to form a *meta-cluster*. The connected computers of a cluster are called *nodes*.

Clusters differ from supercomputers by providing lower communication bandwidth and higher latencies. Similar to supercomputers they provide a homogeneous computing environment in terms of processor architecture, memory amount per node, and operating system.

On the TOP500 list from November 2011 mentioned above, 82% of the machines are cluster systems. They contribute 67.76% of the total computing power on the list. Ten years earlier, these numbers were both below 10%. This shows that cluster systems are more and more widespread. Reasons for their popularity are that cluster systems are relatively cheap and easy to maintain compared to supercomputers while they are nonetheless suitable for scientific computing demands.

Clusters are MIMD architectures. Nevertheless, they are usually programmed in a SPMD fashion in the same way as supercomputers. Clusters are used for dataparallel applications that have a suitable demand for performance in computation and communication.

#### Distributed computing

If the communication distance is very high, usually the term distributed computing is used. This term applies if no guarantee for communication latency or throughput is given. This architecture consists of a number of nodes which are connected by a network. The nodes can be desktop computers or conventional server machines. The Internet or classical Ethernet networks may be used as interconnecting network.

In general, the physical location of the nodes is entirely arbitrary; the nodes may be distributed all over the world. SETI@home [KWA<sup>+</sup>01] was one of the first scientific projects for distributed computing. Its grid computing middleware "BOINC" [And04] is used for many different scientific workloads today.

If the location of the nodes is more restricted, e.g., if the desktop computers of a company are used for parallel computing in the background of daily workload or exclusively at night, the term *office grid* is used. Some companies like Amazon offer distributed computing as *cloud services*.

Distributed computing is a MIMD architecture. It is suitable if the demand for communication is small or if high network latency and low throughput can be compensated or tolerated. This is the case for many data parallel applications. Usually computing resources are used which otherwise would remain unexploited; in case of cloud computing resources can be acquired on demand.

#### 2.2 Parallel programming

The previous section introduced parallel architectures on three different levels of abstraction: the microarchitecture, the instruction set, and the system architecture.

On the level of the microarchitecture, the only way to influence how instructions are executed in parallel is the order in which the instructions are placed in the machine code of the program. For programming languages like C, C++, or Fortran, the order is defined by the compiler; nowadays all optimizing compilers have some heuristics that try to produce a reasonable scheduling of instructions for the requested microarchitecture. If more control over instruction scheduling is needed, e.g. in case the compiler fails to produce efficient machine code, the program (or parts of the program) can be written in assembly language.

Programming in assembly language also gives full control over program execution on the level of the instruction set. In general compilers do not give direct access to the instruction set; however, some compilers allow the programmer to embed assembly code into the program code for this purpose. Compilers for VLIW architectures handle data flow and instruction scheduling internally without direct control of the programmer. Vectorizing compilers can parallelize sequential source code for vector processors in certain cases in an automated fashion. Some programming languages offer SIMD vector operations as part of the language.

On the level of the system architecture, the program is executed by several computing units. The workload of the computation is distributed over these units. Cooperation between the computing units is achieved by communicating intermediate results. The following paragraphs discuss two concepts for communication between the computing units of a parallel system: Either the data is exchanged between computing units implicitly via *shared memory* or explicitly via *message passing*.

#### 2.2.1 Shared memory

Shared memory works like a bulletin board in the lobby of a student dorm: The students place messages on the board. Messages can be read, modified or removed by all students. The location of the board is well known to all students. Students can access the board at any time in any order. Communication over a bulletin board is most efficient if the students have some agreement about what information is placed on what position on the board and who is allowed to remove or modify the information.

From a programming perspective, communication is accomplished by making a certain memory region available to all instances of a program which are executed in parallel. All instances of the program write data to or read data from this memory region. Shared memory programming is available on most parallel system architectures listed in the previous section. However, it fits most naturally to SMP architectures with a joint memory space.

A popular standard for shared-memory programming on SMP architectures is OpenMP (Open Multi-Processing, see [OMP]). OpenMP defines a set of compiler directives for C, C++, and Fortran compilers. These directives instruct the compiler to distribute the workload of the specified code regions over several threads. Since all threads are executed in the same address space, they have full access to all data of the parent process. The compiler automatically inserts code for starting, managing, and stopping of threads. Using OpenMP, sequential code can be parallelized relatively easily by inserting compiler directives into sequential source code.

If OpenMP is not available or does not fit the programming model, the programmer can control the parallel execution on an SMP architecture directly by using, e.g., POSIX (Portable Operating System Interface) threads instead of OpenMP. POSIX threads are in particular useful for implementing task-parallel applications. Shared-memory communication between separate processes is carried out by mapping a joint shared memory segment into the address space of each process. An emerging programming standard for general-purpose computing on GPUs is the C-language derivative OpenCL (Open Computing Language) which also can be used for programming of hybrid SMP and GPU computing systems. See Section 2.3 for details on general-purpose GPU programming and OpenCL.

Shared-memory programming brings the risk of race conditions: Consider a segment of program code where a value in shared memory is incremented by two threads A and B. Each thread first reads the value from the memory location to a register, increments the value, and writes it back to the old memory location. Everything is fine if A and B pass this entire code section one at a time. If these three instructions are processed by both threads at the same time, the resulting value in the shared memory location is undefined: Assume thread A is the first one to read the value, but thread B reads the same value before it is modified and stored by A. After both threads have passed the code segment, the value in shared memory has been incremented by only one instead of two.

To make the code segment work, one must ensure that it is processed atomically, i.e. the code segment must only be entered by a thread while no other thread is currently executing it. The most efficient way to implement this particular example is to use processor instructions that perform the incrementation as an atomic operation—if such an instruction is provided by the instruction set and is accessible through the programming language. Many instruction sets offer several flavors of atomic operations. Access to large critical code sections can be controlled with semaphores, locks, mutexes, or any other control mechanism that is offered by the programming environment or the operating system. For shared-memory programming, the programmer is obliged to provide access control to critical code sections and to guarantee deterministic program behaviour.

#### 2.2.2 Message passing

Message passing is similar to sending a letter by mail: When the sender finished writing the letter, it is picked up by a postman and delivered to the receiver. After the letter has been handed over to the postman, the sender has no access to the letter anymore. The receiver checks his mailbox for incoming mail. At least the address of the receiver needs to be known for successful delivery of the letter.

The message-passing programming paradigm is usually implemented as a library that offers an interface of function calls which can be invoked by the communicating processes. Typically pairs of functions are offered: one for sending, one for receiving a message. Sending and receiving can either be blocking (the sender waits until the postman picks up the letter, the receiver waits until the postman delivers the letter) or non-blocking (the postman picks up and drops off the letter at the mail boxes of sender and receiver while those two are free to continue with their work).

Message passing is available for tightly coupled SMP architectures and for more loosely coupled architectures like clusters; message passing fits most naturally to the latter one. Message passing can compensate for the disadvantages of remote memory access on NUMA architectures for some applications: One process is executed on each NUMA node and message passing is used for the communication between the NUMA nodes.

The most common message-passing interface for high-performance computing is the MPI (Message Passing Interface) standard. This standard defines syntax and semantics of a message-passing interface for the programming languages C and Fortran. Popular implementations of the MPI standard are Open MPI available at [OMPI] and MPICH2 available at [ANL]. Most MPI implementations provide command-line tools and service programs that facilitate starting and controlling MPI processes on large clusters. The performance of communication-intensive applications depends heavily on the capability of the MPI implementation to offer efficient communication on the targeted parallel system.

Communication channels such as pipes or sockets provided by the operating system are more general approaches than MPI. They are commonly used for communication on distributed systems but less commonly on more tightly coupled systems such as clusters or SMP architectures. The operation mode of sockets is particularly useful for applications with a varying number of computing nodes. MPI requires the number of nodes to be fixed over the whole execution time of the application; failing nodes cause the whole computation to be aborted.

#### 2.2.3 Summary

Neither of the two approaches is more expressive than the other: An implementation of the MPI standard might use shared-memory programming for message delivery on an SMP architecture; a distributed shared-memory programming language like Unified Parallel C (UPC, see [LBL]) might use message-passing primitives to keep shared-memory segments coherent on cluster architectures.

The choice between these paradigms depends on the application and its targeted system architecture. The paradigms are not mutually exclusive; hybrid solutions are possible and common on, for example, clusters of SMP architectures. In this case one process (or several processes on NUMA architectures) with several threads is executed on each cluster node. Local communication between the threads is accomplished via shared memory, remote communication between the cluster nodes (and NUMA nodes) via message passing.

#### 2.3 General-purpose GPU programming

Graphics Processing Units (GPUs) are computing devices which are specialized and highly optimized for rendering 3D graphic scenes at high frame rates. Since the 1990s graphics cards have become a mass-market gaming device. Market competition led to a rapid development of computational power alongside a tremendous drop of prices. State-of-the-art GPUs have a single-precision floating-point peak performance in the range of teraflops at relatively small power consumption and moderate prices. Therefore, graphics cards have become more and more attractive for High Performance Computing.

Already in the early '90s the computational power of GPUs has been used for other applications than computer graphics (e.g. [LRD+90]). In 2003, Mark Harris established the acronym GPGPU for the general-purpose use of graphics cards [Har03]. In the beginning, it was very tedious to program GPUs. The algorithm had to be expressed with the shader instructions of the rendering pipeline. General-purpose programmability was greatly increased when NVIDIA introduced a unified shader hardware architecture with the GeForce 8 Series graphics cards in November 2006. NVIDIA made an essential change in the hardware architecture: Instead of implementing several different types of graphic shaders in hardware, they developed a massively parallel multi-core architecture and implemented all shaders in software. NVIDIA's architecture is called Compute Unified Device Architecture (CUDA). In 2007, AMD also released a GPU with a unified shader architecture, the Radeon R600 series.

AMD and NVIDIA both offer software development kits (SDKs) that give access to the GPUs from a host program running on the CPU. The host program controls the execution of a shader program, the so called kernel. NVIDIA's SDK is called "CUDA SDK"; the SDK of AMD was first named "ATI Stream SDK". Nowadays it is promoted as "AMD Accelerated Parallel Processing (APP) SDK". Initially, both vendors used different C-like programming languages, NVIDIA offered a language called CUDA-C, AMD used Brook+, an enhanced version of BrookGPU (see [BFH+04]). Today both vendors support the execution of programs written in OpenCL. OpenCL is a specification of a programming framework consisting of a programming language and an API. It facilitates writing and executing parallel programs in heterogeneous computing environments consisting of e.g. multi-core CPUs and GPUs. The OpenCL specification can be found at [Mun11].

Even though GPUs have been used successfully to accelerate scientific algorithms and workloads (e.g. [BGB10; RRB+08]), their performance can only be fully exploited if the program is carefully optimized for the target hardware. There are also reports of cases where GPUs do not deliver the expected performance (e.g. [BBR10]). Apart from the fact that not all applications are suitable for an efficient implementation on GPUs, there may be several reasons for an underutilization of these computing devices, e.g. poor exploitation of data locality, bad register allocation, or insufficient hit rates in the instruction cache. In particular the latter two cases cannot easily, maybe not at all, be prevented when using a high-level programming language: If the compiler does not deliver a suitable solution there is no chance to improve the performance without circumventing the compiler.

To solve this issue, Bernstein, Schwabe, and I constructed a toolbox for implementing GPU programs in a directly translated assembly language (see Section 2.3.2). The current solution works only with NVIDIA's first generation CUDA hardware. Due to NVIDIA's and AMD's lack of public documentation the support for state-of-the-art GPUs still is work in progress.

Since 2006 NVIDIA released several versions of CUDA. Furthermore, the processor architecture has been modified several times. The architectures are classified by their respective *compute capability*. The first generation of CUDA GPUs has the compute capabilities 1.0 to 1.3 and was distributed until 2010. In 2010, NVIDIA introduced the second generation of CUDA called Fermi. Up to now Fermi cards have the compute capabilities 2.0 and 2.1. Release steps within each generation introduce minor additions to the instruction set and minor extensions to the hardware architecture. The step from 1.3 to 2.0 introduced a completely redesigned hardware architecture and instruction set.

Because CUDA allows major changes of the hardware implementation, CUDA software is usually not distributed in binary form. Instead, the device driver receives the CUDA-C or OpenCL source code or an instruction-set-independent intermediate assembly code called Parallel Thread Execution (PTX). In either case the source code is compiled for the actual hardware and then transferred to the GPU for execution.

NVIDIA does not offer an assembler for CUDA; PTX-code is compiled like a high level language and therefore does not give direct access to instruction scheduling, register allocation, register spills, or even the instruction set. Nevertheless, Wladimir J. van der Laan reverse-engineered the byte code of the first generation CUDA 1.x instruction set and implemented an assembler and disassembler in Python. These tools are available online at [Laa07] as part of the *Cubin Utilities*, also known as *decuda*.

In April 2011, Yun-Qing Hou started a similar project called *asfermi* in order to provide an assembler and disassembler for the instruction set of CUDA 2.x Fermi. Hou's code is available at [Hou11]. Since this tool set does not yet fully support all opcodes of the Fermi architecture, the remainder of this section will focus on decuda and therefore compute capability 1.x and CUDA SDK version 2.3. Support for OpenCL has been introduced with CUDA SDK version 4.0 and will not be described in this section.

#### 2.3.1 Programming NVIDIA GPUs

Today's NVIDIA GPUs are SIMD architectures. They have been designed for data parallel applications—e.g. graphics processing. Each independent item of a data stream is assigned to a thread; many threads are executed in parallel on the execution units of the GPU. A certain number of threads (compute capability 1.x: 32 threads; compute capability 2.x: 64 threads) are executed in lock-step, i.e. a single instruction is fetched and executed by all of these threads. Such a group of threads is called a thread warp. Threads in a warp are allowed to take different branches but this results in a sequential execution of the branches that are taken by subsets of threads and therefore in a loss of efficiency. Several warps can be organized in a thread block. All threads in a thread block can exchange data via a fast data storage called shared memory. Several thread blocks can be executed concurrently on one GPU core and in parallel on different cores.

Each core has a large number of registers and a relatively small amount of shared memory, e.g. on compute capability 1.3 devices each core has 16384 registers and 16 KB shared memory. A set of registers is assigned to each thread and a fraction of shared memory to each thread block for the whole execution of the thread block. Therefore, the maximum number of threads that can be executed concurrently on one core depends on the number of registers each thread demands and the amount of shared memory each thread block requests.

Since each core of compute capability 1.x GPUs has 8 ALUs, one warp of 32 threads seems to be more than enough to keep all ALUs busy. Nevertheless, experiments showed that one single warp is scheduled only every second instruction issue cycle (which is four times longer than one ALU clock cycle), leaving the ALUs idle during one issue cycle in between. Consequently at least two warps should be executed per core. Furthermore, the instruction set can only address 128 registers, so to fully utilize all registers at least 128 threads (four warps) must be executed concurrently. In addition, instruction latencies and memory latencies lead to the recommendation of running at least 192 threads concurrently to get a high ALU utilization [NVI09a].

The threads have access to off-chip device memory, also called *global memory*; this memory is not cached close to the cores. Furthermore, there is a *constant memory* cache for read-only data access. The cores also have access to a texture memory which is not further investigated in this thesis. Communication between thread blocks is only possible via global memory. Compute capabilities 1.1 and above offer atomic operations on global memory for synchronization between thread blocks.

As stated above, NVIDIA graphics cards can be programmed with the help of the CUDA-SDK. The goal of CUDA is that programmers do not need to rewrite their whole application to profit from the computational power of GPUs. Instead, computationally intensive parts from an existing program are identified and delegated to the GPU. It is possible to mix host code and device code in the source code. To distinguish between the two different execution domains, NVIDIA introduced a small set of additional keywords to the C programming language [NVI09b].

Three Function Type Qualifiers specify in which context a function should be executed: A \_\_host\_\_ function can only be called from and executed on the host. This is the standard qualifier, therefore it can be omitted. A \_\_global\_\_ function is executed on the device and can be called from the host. Functions which are executed on the device and can only be called from the device are specified as \_\_device\_\_ functions.

The memory location of data is defined by three Variable Type Qualifiers. Variables which are defined with the keyword \_\_device\_\_ are located on the device. The additional keyword \_\_constant\_\_ specifies data items that are not changed during kernel execution and can be cached in the constant data cache of the GPU cores. Variables that should reside in shared memory are defined as \_\_shared\_\_. Similar specifiers are available for PTX code to qualify global or shared memory accesses. The CUDA API offers functions to move data between host and device memory.

The CUDA-C compiler is called *nvcc*. It slightly modifies the host code to be compliant to standard C and passes this code to the default C compiler, e.g. gcc. The kernel code is extracted and compiled to PTX-code and machine-code if requested.

When the kernel is invoked through the CUDA API during program execution, the CUDA runtime tries to locate a kernel binary that fits to the actual GPU hardware. If no binary is available, either CUDA-C or PTX source code is used to compile the kernel. The binary can afterwards be stored in a code repository for future usage to avoid recompilation at each invocation.

Experiments showed that NVIDIA's compiler nvcc is not suitable for scientific workloads. In particular the register allocator of nvcc produced inefficient binary code for cryptanalytic kernels. The allocator seems to be optimized for small kernels (since most shader kernels are relatively small) and does not perform well on kernels that have several thousand lines of code. In some cases the compiler ran for several hours, eventually crashing when the system ran out of memory. When the compiler succeeded to produce assembly code, the program required a high number of registers; register spills occurred frequently. Since spilled registers are not cached close to the core but written to and read from global memory, this causes high instruction latencies and therefore often results in performance penalties.

These issues can be solved by writing cryptographic computing kernels by hand in assembly language using van der Laans assembler cudasm. The following section describes the toolkit *qashm-cudasm* that helps to implement and maintain kernels of several thousand lines of assembly code.

#### 2.3.2 Assembly for NVIDIA GPUs

The key to programming kernels for NVIDIA GPUs in assembly language is the assembler cudasm available at [Laa07]. It translates a kernel written in assembler into a text file containing the byte code in a hexadecimal representation. The assembly language was defined by van der Laan to use the same mnemonics and a similar syntax as the PTX code of NVIDIA whenever possible.

The output file of cudasm can be put into the code repository of the CUDA application. The CUDA runtime transfers it to the graphics card for execution the same way as a kernel that was compiled from CUDA-C or PTX. The following tweaks and compiler flags are necessary to make the CUDA runtime digest the cudasm-kernel:

First a host application is written in CUDA-C. This application allocates device memory, prepares and transfers data to the graphics card and finally invokes the kernel as defined by the CUDA API. The device kernel can be implemented in CUDA-C for testing purposes; if this is omitted a function stub for the kernel must be provided. Eventually, the program is compiled using the following command:

nvcc -arch=architecture -ext=all -dir=repository sourcefiles -o outfile

The desired target architecture can be chosen by the flag arch; e.g. compute

capability 1.0 is requested by arch=sm\_10, compute capability 1.3 by arch=sm\_13.

The flag ext=all instructs the compiler to create a code repository for both PTX

and assembly code in the directory repository. For each run nvcc will create

a separate subdirectory in the directory of the code repository; the name of the

subdirectory seems to be a random string or a time based hash value. The runtime

will choose the most recent kernel that fits to the actual hardware. Deleting all

previous subdirectories when recompiling the host code facilitates to keep track

of the most recent kernel version.

The PTX kernel will be placed inside the newly created subdirectory in the file  $compute\_architecture$ . The binary code resides in the file  $sm\_architecture$ . The latter one can simply be replaced by the binary that was created by cudasm. The runtime library will load this binary at the next kernel launch.

#### Assembly programming

Commercial software development requires a fast, programmer friendly, efficient, and cheap work flow. Source code is expected to be modular, reusable, and platform independent. These demands are usually achieved by using high-level programming languages like C, C++, Java, C#, or Objective-C. There are only a few reasons for programming in assembly language:

- high demands on performance: In many cases hand-optimizing critical code sections gives better performance than compiler-optimized code. This has several reasons; details can be found in [Sch11a, Section 2.7].

- the need for direct access to the instruction set: Some instructions like the AES instruction set [Gue10] might not be accessible from high level programming languages. Operating systems need access to special control instructions.

- the requirement for full control over instruction order: For example the program flow of cryptographic applications can leak secret information to an attacker [Koc96]. This can be avoided by carefully scheduling instructions by hand.

• a questionable understanding of "having fun": Some people claim that it is fun to program in assembly language.

Only the latter one might allow the programmer to actually enjoy programming in assembly language. Assembly programming is a complex and error prone task. To reduce the complexity of manually writing GPU assembly code, this section introduces several tools that tackle key issues of assembly code generation.

The major pitfall of writing assembly code is to keep track of what registers contain which data items during program execution. On the x86 architecture which provides only 8 general purpose registers, this is already troublesome. Keeping track of up to 128 registers on NVIDIA GPUs pushes this effort to another level. However, the advantage to choose what register contains which data at a certain time when running the program is not necessary to write highly efficient assembly code and therefore is usually not the reason for writing assembly code in the first place. As long as the programmer can be sure that a register allocator finds a perfect register allocation provided that it exists and otherwise reports to the programmer, register allocation can be delegated to a programming tool. However, this tool should not be NVIDIA's compiler nvcc—since it neither finds a perfect register allocation nor reports on its failure.

Furthermore, there is no common syntax for different assembly languages; even for the same instruction set the syntax may be different for assemblers of different vendors: e.g. "addl %eax, -4(%rbp)" and "add DWORD PTR [rbp-4], eax" are the same x86 instruction in gcc assembler and Intel assembler, respectively. The instructions vary in mnemonic, register and addressing syntax, and even in operand order. Therefore switching between architectures or compilers is error prone and complicated. Furthermore, most assembly languages have not been designed for human interaction and are not easily readable. This again is not an inherent problem of assembly programming itself but a shortcoming of commonly used assembly programming tools.

Both of these pitfalls, register allocation and syntax issues, are addressed by Daniel J. Bernstein's tool qhasm.

#### qhasm

The tool qhasm is available at [Ber07b]. It is neither an assembler itself nor has it been designed for writing a complete program; qhasm is intended to be used for replacing critical functions of a program with handwritten assembly language. The job of qhasm is to translate an assembly-like source code, so called *qhasm code*, into assembly code. Each line in qhasm code is translated to exactly one assembly instruction. The syntax of the qhasm code is user-defined. Furthermore, qhasm allows using an arbitrary number of named register variables instead of the fixed number of architecture registers in the qhasm code. These register variables are mapped to register names by the register allocator of qhasm. If qhasm does not find a mapping, it returns with an error message; the programmer is in charge of spilling registers to memory. The order of instructions is not modified by qhasm.

Therefore, qhasm gives as much control to the programmer as writing assembly directly while eliminating the major pitfalls.

The input for qhasm is the qhasm code consisting of variable declarations and operations and a *machine description file*. This file defines the syntax of the qhasm code by providing a mapping of legitimate qhasm operations to assembly instructions. Furthermore, it contains information about the calling convention and the register set of the target environment.

This design allows the programmer to easily adapt qhasm to new machine architectures by providing an appropriate machine description file. Furthermore, qhasm code for different architectures can follow a unified, user defined syntax. In theory qhasm source code can be reused on other architectures if the instruction sets offer instructions of identical semantics and if a consistent machine description file is provided; nevertheless, it is likely that parts of the qhasm code need to be rewritten or reordered to take architectural differences into account and to achieve full performance.

#### qhasm-cudasm

Van der Laan's assembler cudasm combined with Bernstein's register allocator qhasm (together with a machine description file that was written for cudasm) gives a powerful tool for programming NVIDIA graphics cards on assembly level and can be easily used for small kernels. Nevertheless, for large kernels of several hundred or even thousand lines of code additional tools are necessary to gain a reasonable level of usability for the following reasons:

NVIDIAs compiler nvcc does not support linking of binary code; usually all functions that are qualified with the keyword <code>\_\_device\_\_</code> in CUDA-C are inlined before compiling to binary code. Therefore it is not possible to replace only parts of a CUDA-C kernel with qhasm code—the whole GPU kernel must be implemented in qhasm code. But qhasm was designed to replace small computationally intensive functions. There is no scope for register variables: the names of register variables are available in the whole qhasm code. This makes it complicated to keep track of the data flow. Furthermore, qhasm does not support the programmer in maintaining a large code base e.g. by splitting the code into several files.

Therefore, a modified version of the m5 macro processor is used on top of qhasm to simplify the handling of large kernels. The original version of m5 by William A. Ward, Jr. can be found at [War01]. The following list gives an overview of some native m5 features:

- includes: An m5 source file can include other m5 files; the content of the files is inlined in the line where the include occurs.

- functions: Functions can be defined and called in m5; "call" in this case means that the content of the called function is inlined at the position where the call occurs.

- expressions: Macro variables can be defined in m5 and expressions on macro variables and constant values can be evaluated.

- loops: Loops over macro variables result in an "unrolled" m5 output.

The m5 macro processor was extended to support scoping of register variables. Register variables which are defined in a local scope are automatically prefixed by m5 with a scope-specific string. This guarantees locality on the qhasm level.

The m5 macro processor completes the qhasm-cudasm development toolkit. Each kernel is processed on three levels: The programmer provides a set of source files with the file extension ".mq". Each mq-file contains qhasm code enriched with m5 macro instructions. These files are flattened by m5 to a single qhasm file with the file extension ".q". The qhasm code is fed to qhasm together with the machine description file. The output of qhasm is an assembly file with the file extension ".s". Eventually the assembly file is processed by cudasm, giving the final binary file with the file extension ".o". This file is used to replace the kernel stub that was created by nvcc in the code repository directory.

The solution of using m5 for preprocessing is not perfect; in particular the syntax for declaring and using local register variables is error-prone. Therefore in the future several functionalities of m5 will be integrated into qhasm, in particular function inlining and the declaration of local register variables.

Furthermore, future versions of qhasm-cudasm will support up-to-date graphics hardware of NVIDIA and AMD, using either the upcoming assembler implementations of the open-source community or by contributing assemblers ourselves. As mentioned before the open-source project asfermi aims at providing an assembler for NVIDIA's Fermi architecture. Ádám Rák started to implement an assembler for AMD graphics cards as open-source software (available at [Rák11]). Furthermore, an initial version of an assembler for AMD graphics cards is provided on my website at [Nie11]. Since AMD uses a VLIW architecture, additional tools or extensions to qhasm are necessary for programming AMD graphics cards in assembly language.

The combination of qhasm and cudasm together with m5 was used for programming a large cryptographic kernel of over 5000 lines of code. This project is described in Chapter 3. Furthermore, various kernels for benchmarking NVIDIAs GeForce 200 Series GPUs were implemented using these tools.

## 3

### Parallel implementation of Pollard's rho method

The elliptic-curve discrete-logarithm problem (ECDLP) is the number-theoretic problem behind elliptic-curve cryptography (ECC): the problem of computing a user's ECC secret key from his public key. Pollard's rho method solves this problem in  $O(\sqrt{\ell})$  iterations, where  $\ell$  is the largest prime divisor of the order of the base point. A parallel version of the algorithm due to van Oorschot and Wiener [OW99] provides a speedup by a factor of  $\Theta(N)$  when running on N computers, if  $\ell$  is larger than a suitable power of N. In several situations a group automorphism of small order m provides a further speedup by a factor of  $\Theta(\sqrt{m})$ . No further speedups are known for any elliptic curve chosen according to standard security criteria.

However, these asymptotic iteration counts ignore many factors that have an important influence on the cost of an attack. Understanding the hardness of a specific ECDLP requires a more thorough investigation. The publications summarized on [Gir11], giving recommendations for concrete cryptographic key sizes, all extrapolate from such investigations. To reduce extrapolation errors it is important to use as many data points as possible, and to push these investigations beyond the ECDLP computations that have been carried out before.

Certicom published a list of ECDLP challenges in 1997 at [Cer97] in order to "increase the cryptographic community's understanding and appreciation of the difficulty of the ECDLP". These challenges range from very easy exercises, solved in 1997 and 1998, to serious cryptanalytic challenges. The last Certicom challenge that was publicly broken was a 109-bit ECDLP in 2004. Certicom had already predicted the lack of further progress: it had stated in [Cer97, page 20]

that the subsequent challenges were "expected to be infeasible against realistic software and hardware attacks, unless of course, a new algorithm for the ECDLP is discovered."

Since then new hardware platforms have become available to the attacker. Processor design has moved away from increasing the clock speed and towards increasing the number of cores. This means that implementations need to be parallelized in order to make full use of the processor. Running a serial implementation on a recent processor might take longer than five years ago, because the average clock speed has decreased, but if this implementation can be parallelized and occupy the entire processor then the implementation will run much faster.

Certicom's estimate was that ECC2K-130, the first "infeasible" challenge, would require (on average) 2 700 000 000 "machine days" of computation. The main result of this chapter is that a cluster of just 1066 NVIDIA GTX 295 graphics cards or 2636 PlayStation 3 gaming consoles would solve ECC2K-130 in just one year; therefore nowadays this challenge requires only 379 496 machine days on a graphics card or 938 416 machine days on a gaming console.

The research presented in this chapter is joint work with Bos, Kleinjung, and Schwabe published in [BKN<sup>+</sup>10] as well as with Bernstein, Chen, Cheng, Lange, Schwabe, and Yang published in [BCC<sup>+</sup>10]. It is also included in the PhD thesis of Schwabe [Sch11a, Chapter 6]. Furthermore it is part of a large collaborative project that has optimized ECDLP computations for several different platforms and that aims to break ECC2K-130. See [BBB<sup>+</sup>09] and [Ano] for more information about the project. This research has been supported by the Netherlands National Computing Facilities foundation (NCF) as project MP-185-10.

This chapter is structured as follows: Section 3.1 and Section 3.2 briefly introduce Pollard's rho method and the iteration function of this method for ECC2K-130. Section 3.3 gives a detailed description of the implementation for the Cell processor and section 3.4 for the GTX 295 graphics card. Section 3.5 will conclude with a comparison of both implementations.

## 3.1 The ECDLP and the parallel version of Pollard's rho method

The standard method for solving the ECDLP in prime-order subgroups is Pollard's rho method [Pol78]. For large instances of the ECDLP, one usually uses a parallelized version of Pollard's rho method due to van Oorschot and Wiener [OW99]. This section briefly reviews the ECDLP and the parallel version of Pollard's rho method.

The ECDLP is the following problem: Given an elliptic curve E over a finite field  $\mathbb{F}_q$  and two points  $P \in E(\mathbb{F}_q)$  and  $Q \in \langle P \rangle$ , find an integer k such that Q = [k]P.

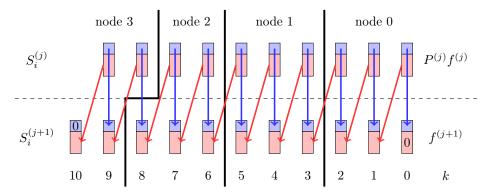

Let  $\ell$  be the order of P, and assume in the following that  $\ell$  is prime. The parallel version of Pollard's rho method uses a client-server approach in which each client does the following:

- 1. Generate a pseudo-random starting point  $R_0$  as a known linear combination of P and Q:  $R_0 = a_0P + b_0Q$ ;

- 2. apply a pseudo-random iteration function f to obtain a sequence  $R_{i+1} = f(R_i)$ , where f is constructed to preserve knowledge about the linear combination of P and Q;

- 3. for each i, after computing  $R_i$ , check whether  $R_i$  belongs to an easy-to-recognize set D, the set of distinguished points, a subset of  $\langle P \rangle$ ;

- 4. if at some moment a distinguished point  $R_i$  is reached, send  $(R_i, a_i, b_i)$  to the server and go to step 1.

The server receives all the incoming triples (R, a, b) and does the following:

- 1. Search the entries for a *collision*, i.e., two triples (R, a, b), (R', a', b') with R = R' and  $b \not\equiv b' \pmod{\ell}$ ;

- 2. obtain the discrete logarithm of Q to the base P as  $k = \frac{a'-a}{b-b'}$  modulo  $\ell$ .

The expected number of calls to the iteration function f is approximately  $\sqrt{\pi\ell/2}$  assuming perfectly random behavior of f. Therefore the expected total runtime of the parallel version of Pollard's rho algorithm is  $\sqrt{\pi\ell/2} \cdot t/N$  given the time t for executing one step of iteration function f and N computing devices.